Дисциплина: «Электротехника и электроника»

Цель работы: Изучение принципов функционирования и использования

дискретных логических элементов и триггеров, относящихся к транзисторно-транзисторной логике (ТТЛ), изучение взаимозаменяемости триггеров различных типов.

Рабочее задание:

— Экспериментально исследовать работу логических элементов и триггеров

Расчетное задание:

— Составить таблицы истинности для каждого исследуемого элемента.

1. Выполнение рабочего задания.

1.1. Собираем схему исследуемого элемента.

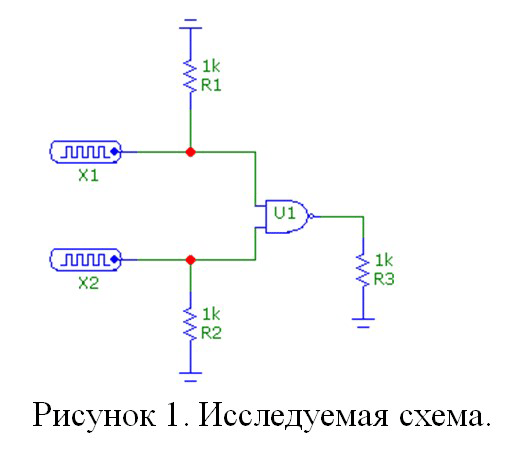

Результат приведен на рисунке 1.

Рисунок 1. Исследуемая схема.

Получаем временные диаграммы исследуемой схемы (рисунок 2).

Рисунок 2. Временные диаграммы логического элемента 2 И-НЕ

Согласно временных диаграмм уровень логической «1» составляет 3 В.

Временные диаграммы соответствуют выполняемой элементом функции.

1.2. Собираем схему исследуемого элемента.

Результат приведен на рисунке 3.

Рисунок 3. Исследуемая схема.

Получаем временные диаграммы исследуемой схемы (рисунок 4).

Рисунок 4. Временные диаграммы логического элемента 2 ИЛИ-НЕ

Согласно временных диаграмм уровень логической «1» составляет 3 В.

Временные диаграммы соответствуют выполняемой элементом функции.

1.3. Собираем схему исследуемого элемента.

Результат приведен на рисунке 5.

Рисунок 5. Исследуемая схема.

Получаем временные диаграммы исследуемой схемы (рисунок 6).

Рисунок 6. Временные диаграммы синхронного JK-триггера

Согласно временных диаграмм уровень логической «1» составляет 3 В.

Временные диаграммы соответствуют выполняемой элементом функции.

1.4. Собираем схему исследуемого элемента.

Результат приведен на рисунке 7.

Рисунок 7. Исследуемая схема.

Получаем временные диаграммы исследуемой схемы (рисунок 8).

Рисунок 8. Временные диаграммы синхронного D-триггера

1.5. Собираем схему исследуемого элемента.

Результат приведен на рисунке 9.

Рисунок 9. Исследуемая схема.

Получаем временные диаграммы исследуемой схемы (рисунок 10).

Рисунок 10. Временные диаграммы синхронного Т-триггера

1.6. Собираем схему исследуемого элемента.

Результат приведен на рисунке 11.

Рисунок 11. Исследуемая схема.

Получаем временные диаграммы исследуемой схемы (рисунок 12).

Рисунок 12. Временные диаграммы асинхронного Т-триггера

2. Расчетное задание.

Таблица истинности для логического элемента 2И-НЕ

Таблица истинности для логического элемента 2ИЛИ-НЕ

Таблица истинности для JK — триггера

Таблица истинности для синхронного D — триггера

Таблица истинности для синхронного T — триггера

Таблица истинности для асинхронного T — триггера

Проработанная литература:

1. Цифровая электроника (полный курс): Учебник для вузов. Под

редакцией О.П. Глудкина. — М.: Горячая линия — Телеком, 2003. —

768с. (§§14.1-14.6, стр. 504-517; §§17.1-17.2, стр. 553-562).

2. Лачин В.И., Савелов Н.С. Электроника: Учеб. пособие. —

Ростов н/Д: изд-во «Феникс», 2000. — 448с. (§3.3, стр. 323-337; §3.5,

стр. 355-364).

3. Кузовкин В.А. Электроника. — М.: Логос, 2005. — 328с. (§§ 6.1-

6.3, стр. 99-121; §8.2, стр. 133-139).

4. Миловзоров О.В., Панков И.Г. Электроника. — М.: ВШ, 2005. —

288с. (§§3.1, 3.2, стр.109-121; §3.4, стр.130-132; §3.9, стр.153-159).

Лабораторная ЭВ4 Исследование дискретных логических элементов и триггеров № 200405-4

Цена 350 р.